Characteristics

The

machine instructions or computer instructions is a processor

operation which determined by the execution of the instructions. The collection

of different instructions that the processor can execute is referred to as the

processor’s instruction set.

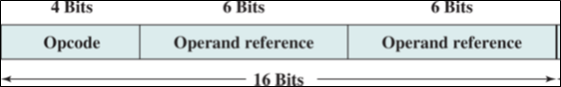

The

processor required the information provided by each instruction for execution.

There are four elements of instructions; operation code, source operand

reference, result operand reference and next instruction reference. Operation code or

opcode specifies the operation to

be performed (e.g., ADD, I/O). The operation is specified by a binary code. The

source operand reference in the

operation may involve one or more source operands that are inputs for the

operation. Result operand reference

becomes the reference for operation after produce a result. Lastly, next instruction reference that tells

the processor the location to fetch the next instruction after the execution of

current instruction complete.

The

source and result operands consist of main or virtual memory, processor

register, immediate and input/output device.

Format, Type, Number and Address

|

Opcode

|

Description

|

|

ADD

|

Add

|

|

SUB

|

Subtract

|

|

MUL

|

Multiply

|

|

DIV

|

Divide

|

|

LOAD

|

Load

data from memory

|

|

STOR

|

Store

data to memory

|

Most

computers fall into one of the following types of CPU organization:

i.

Single

Accumulator organization: ADD X

AC ® AC + M [×]

ii.

General

Register Organization: ADD R1,

R2, R3 R ® R2 + R3

iii.

Stack

Organization: PUSH

X

Following are the address instructions in

computer:

i.

Three address instruction

Computer with three

addresses instruction format can use each address field to specify either

processor register is memory operand.

For example:

|

ADD R1, A,

B R1 ® M [A] + M [B]

|

|

|

|

ADD R2, C,

D R2 ® M [C] + M [D]

|

|

X

= (A + B) * (C + D)

|

|

MUL X, R1, R2 M [X] R1 *

R2

|

|

|

ii.

Two address instruction

Most common in commercial computers. Each address field can specify

either a process register on a memory word.

For example:

|

MOV

|

R1, A

|

R1 ® M [A]

|

|

|

ADD

|

R1,

B

|

R1 ® R1 + M [B]

|

|

|

MOV

|

R2,

C

|

R2 ® M

[C]

|

X = (A + B) * ( C + D)

|

|

ADD

|

R2,

D

|

R2 ® R2 + M [D]

|

|

|

MUL

|

R1,

R2

|

R1 ® R1 * R2

|

|

|

MOV

|

X,

R1

|

M [X] ® R1

|

|

iii.

One address instruction

It used an implied

accumulator (AC) register for all data manipulation. For

multiplication/division, there is a need for a second register.

|

LOAD

|

A

|

AC ® M [A]

|

|

|

ADD

|

B

|

AC ® AC + M [B]

|

|

|

STORE

|

T

|

M [T] ®

AC

|

X = (A +B) × (C + A)

|

|

LOAD

|

C

|

AC ® M [C]

|

|

|

ADD

|

A

|

AC ® AC + M [A]

|

|

|

MUL

|

T

|

AC ® AC + M [T]

|

|

|

STORE

|

X

|

M[X] = AC

|

|